Toshiba Information Systems (Japan) Corporation

Logic design and verification Overview

Considerably shortened period of system design [High-level design and verification (ESL)]

We introduced high-level design methodology in 2002 and have accumulated numerous practical results and experience. Using technologies of modeling, verification environment construction and high-level synthesis (HLS), simulation models are created at abstraction levels depending on the purpose, which significantly reduces the system design period and leads to a coherent design service ranging from algorithm study to the consideration and proposal of hardware implementation and high-level synthesis. The installation of the environment, construction support and verification services are also provided.

Model-based design

Various modeling technology

- I/O, image and sound, etc.

- Estimate of HW performance

- Selection of optimal design method

Verification environment construction technology for system consideration

- Architecture investigation

- HW/SW co-validation

- Bus performance analysis

High-level synthesis

Description methodology depending on the design object

- Large-scale computing system

- Control system

- Cryptographic processing system

Abundant experience with tool usage

Synthesis methodology according to the required performance

- Circuit area reduction

- Operation speed improvement

- Lower power consumption

Languages

C/C++, System C, Model language

Solution · Features

- Creation of simulation models at abstraction levels according to the purpose

- Cost reduction and shortened development period by model-based development

- High-level synthesis technology to convert functions in System C or C++ to RTL

- High speed simulation

- High abstraction level

- High accuracy optimal design

- Predictable system performance

- High efficiency RTL generation of large sand complex algorithm

- Fast silicon

To satisfy both high quality and a short delivery time [Logic design and verification]

Toshiba Information Systems has expertise and experience to support customers in each stage of ASIC design, including feasibility verification of design specifications, estimation of the optimal architecture, environment setting for development, IP integration and leading-edge verification techniques. We precisely understand various design intentions from block to chip levels to minimize iteration. ASIC solutions to achieve a good balance between complex, high performance properties and a short commercialization period are provided.

- Design services

-

- Engineering Proposals

- Feasibility Studies & Technology Assessment

- System Architecture and Design

- Functional Design Specifications

- System Test Procedures and support

- Prototype debug and system integration

- IP selection (including Third Party IP)

- Block Partitioning RTL implementation

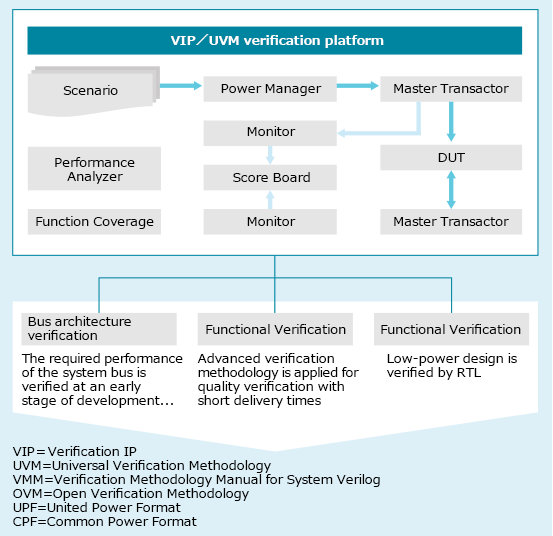

- Verification services

-

- Functional Verification (Block and Top level)

- Assertion-based verification(ABV)

- Formal verification

- code coverage, functionality coverage

- Power aware simulation

- Random and direct testing, object Oriented programming, Gate Level simulation, RTL vs. gates simulation

- Expert level expertise in UVM, OVM, VMM, eRM, SVA and other verification methodologies

- Methodologies: UVM, OVM, VMM

- Tools: NC-Verilog, VCS, QuestaSim

- Languages: SystemVerilog, SystemC, C++, OpenVera, Specman/e and VHDL