高位設計/検証 概要

システム設計の期間を大幅に短縮【高位設計/検証(ESL)】

「検証だけでなくシステム設計の期間も大幅に短縮したい」というお客様からのご要望を受け、当社では2002年から高位設計手法を導入しています。モデリング技術、検証環境構築技術、高位合成(HLS) 技術を用いて、目的に応じた抽象度のシミュレーションモデルを作成、システム設計の期間短縮を実現します。

* ESL:Electronic System Level

* HLS:High Level Synthesis

モデルベース設計

多様なモデリング技術

- I/O系、画像音声系など

- HW性能見積もり

- 最適な設計手法の選択

システム検討のための検証環境構築技術

- アーキテクチャ探索

- HW/SW協調検証

- Busパフォーマンス測定

高位合成

設計対象に応じた記述ノウハウ

- 大規模演算系

- 制御系

- 暗号処理系

- EdgeAI

豊富なツール活用経験

要求性能に応じた合成ノウハウ

- 回路面積縮小

- 動作速度向上

- 低消費電力化

対応言語

SystemC、C/C++、モデル言語

ソリューション・特長

- 目的に応じた抽象度のモデル作成

- モデルベース開発

- SystemC やC++ で記述した機能をハードウェア(RTLに変換) 化

高品質と短納期を両立するために【ロジック設計/検証】

東芝情報システムは20年以上にわたるロジック設計/検証の経験と、豊富な開発実績を持っています。ASICから大規模SoC開発まで、開発規模、難易度に応じて最適なプロジェクトを組むことができます。

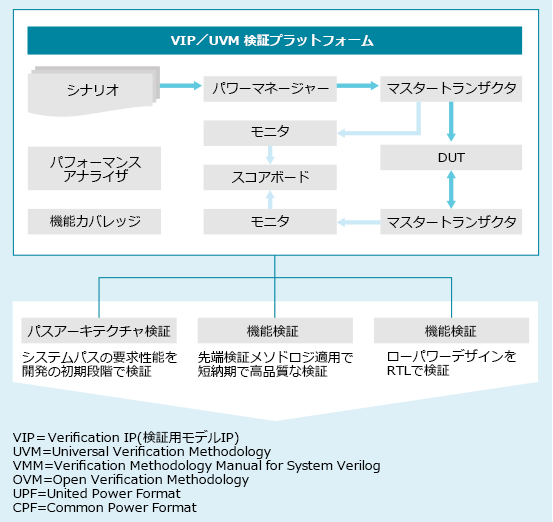

特にロジック検証は近年の回路大規模化に伴い、設計した回路の検証に要する作業量が膨大となっています。効率的に検証を行い、【高品質】と【短納期】を両立する。この二つの課題を高いレベルで解決するために、様々なソリューションをご用意しています。

ソリューション

システム・ブロックレベル検証

- 機能検証

-

- アサーションベース検証

- ランダム検証

- カバレッジドリブン検証

- UPF・CPF をサポート

- UVM・VMM・OVM 先端検証

メソッドをサポート

- 静的検証

-

- 形式検証

特長

- 様々な検証目的に適応するプラットフォームを用意

-

- 各種検証コンポーネント(VIP) が利用可能

- 再利用性の向上

- テストベンチの資産化